五部门关于开展2024年新能源汽车下乡活动的通知

在高带宽传感器应用中隔离 SPI

在高带宽传感器应用中隔离 SPISPI(串行外设接口)总线是设计人员的,原因有很多。SPI 总线可以高速运行,在电路板上的芯片之间等短距离内以高达 60Mbps 的速度传输数据。总

SPI(串行外设接口)总线是设计人员的,原因有很多。SPI 总线可以高速运行,在电路板上的芯片之间等短距离内以高达 60Mbps 的速度传输数据。

总线在概念上很简单,由一个时钟、两条数据线和一个片选信号组成。由于数据在时钟的一个相位上呈现并在相反的相位上读回,因此在速度上存在很大的延迟和不匹配余量。,由于 SPI 总线由单向线路组成,它通过消除流量控制问题简化了微处理器中的实施。由于大多数传统隔离设备是单向的,因此 SPI 总线非常适合使用光耦合器或数字隔离器进行隔离。

在热或压力监测系统等工业应用中,与传感器前端中的 ADC 通信不需要高采样率,因此不需要高 SPI 时钟速率。即使是隔离设计也很容易在各种隔离技术中实现。

但需求随着时间的推移而变化,古老的 SPI 接口已被具有长布线、高数据速率和隔离要求的应用推向极限。在本文中,我们将了解 SPI 总线、它的限制以及如何在隔离系统中处理它们。

推动隔离式 SPI 性能极限的应用是高动态范围传感器接口。要创建具有宽动态范围的系统,设计人员将从具有良好信噪比 (SNR) 的模数转换器 (ADC) 着手,这通常与字长有关。16 位字很常见,在需要更高动态范围的情况下,可以采用其他技术,例如输入的可变增益放大和过采样。过采样将以带宽换取噪声抑制。

如果采样频率加倍,通常噪声性能会提高 3 dB。因此,例如,75 倍的过采样率将使噪声性能和动态范围提高约 18 dB。75 倍的信号过采样意味着以 900 ksps 运行的 ADC 将在大约 6 kHz 的带宽上提供更好的 18 dB 动态范围。带宽和动态范围当然可以权衡取舍,但终,尽可能快地运行 ADC 有很大的好处。

这意味着 SPI 总线将不得不跟上这种雪崩式的数据。让我们考虑一个示例,其中包含用于高采样率应用的典型组件,例如 ADI AD7985 脉冲星 ADC,它可以运行高达 2.5 Msps。我们将看到通过 SPI 总线与其通信如何影响信号链的性能。

ADC 接口

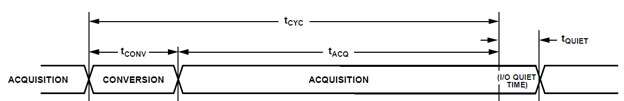

典型的 ADC 在两个基本操作中处理数据(图 1)。首先,ADC 有一个转换周期 (t CONV ),在此期间它创建一个表示其输入端电压的数字字。然后,ADC 在采集时间 (t ACQ )期间通过数字接口将此字传输到控制器。ADC在开始另转换之前通常有一个周期时间 (t CYC ),它大约是 t CONV 和 t ACQ 的总和。有时 t CYC 更短,如果 ADC 有特殊的传输模式,让采集和传输重叠。为简单起见,以下讨论假定顺序转换和采集。

无论数据如何传输,转换时间和循环时间都是相同的。但采集时间取决于数据接口的属性,在大多数情况下是 SPI 总线的操作。如果采集时间由于 SPI 时钟速率而延长,则 ADC 的采样率可能会受到严重限制。

SPI 时钟速率限制

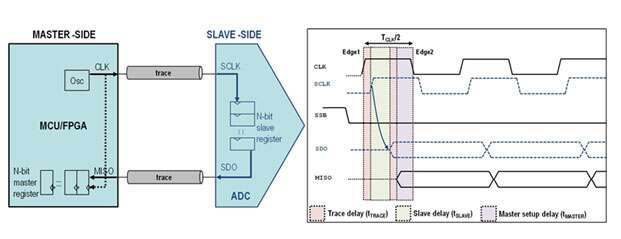

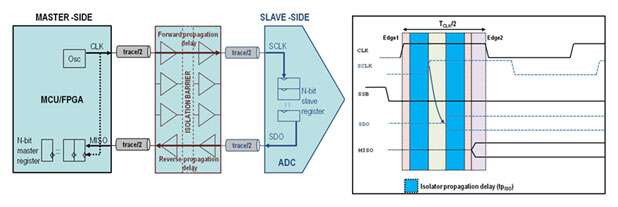

微处理器/FPGA (MCU) 和 ADC 之间的 SPI 链路如图2所示。SPI 总线由一对移位寄存器之间的连接组成,一个在主 MCU 中,一个在从 ADC 中。MCU 提供同步传输的时钟。时钟的一个边沿将数据移出移位寄存器,互补边沿为已呈现在环形拓扑中每个移位寄存器另一端的数据提供时钟。在 ADC 的情况下,可能不需要将数据从 MCU 转移到 ADC,因此为简单起见,这个通道连同从属选择被取消了。ADC 在操作的转换阶段填充其内部移位寄存器,然后在采集阶段将寄存器移出。

在 SPI 事务中,主机生成的时钟信号通过一些布线延迟传输到从机,在一些内部延迟后触发从机移出其数据。数据信号通过布线延迟再次传回主机,它必须在时钟的互补边沿及时到达主机。主机通常有一些额外的设置时间要求。

图 2 显示了这些延迟如何确定半个主时钟周期的短时间。在非隔离系统中,这些延迟通常非常短,在大多数情况下 <10 nS,允许 SPI 时钟以超过 50 MHz 的速度运行。如果将隔离屏障添加到 SPI 数据路径(图 3),它会将传播延迟(prop delay,tp ISO )项添加到跟踪延迟中。隔离器支撑延迟可能超过 100 nS,具体取决于所使用的隔离技术。图 3 显示了额外的隔离器延迟时间如何延长数据处理所需的时间并显着增加 SPI 时钟所需的半周期。隔离延迟支配系统中的所有其他时间延迟,时钟频率可降至几 MHz。

时钟周期的主要限制是要求数据在下一个时钟边沿之前出现在主机中。在非隔离系统中,这不是一个很大的限制,它实际上通过允许大量的时序余量增加了数据传输的稳健性。然而,一旦数据路径的传播延迟开始主导半周期,它会严重降低总线的速度,从而限制具有长隔离器传播延迟的隔离系统中的吞吐量。

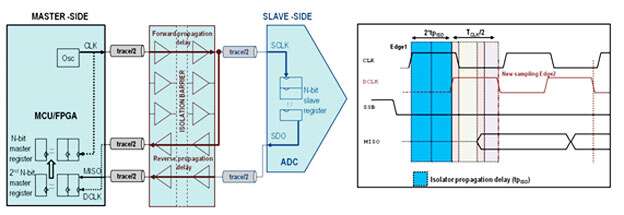

幸运的是,有一种方法可以绕过这个限制。如果从机返回的数据有一个独立的时钟与之同步,则可以在MCU中设置一个单独的接收移位寄存器来接收基于独立时钟的数据。在这种情况下,SPI 总线的吞吐量不再受隔离层传播延迟的限制,而是受隔离器吞吐量的限制。

通过向隔离器添加数据通道并发送隔离 SPI 时钟的副本以及 ADC 数据,可以轻松创建独立时钟 DCLK(图 4 )。“SPI 时钟”路径中的隔离器延迟与“ADC 数据”路径中的隔离器延迟匹配,有效防止隔离器延迟限制所需的 SPI 时钟周期。相反,该周期仅受较短延迟的限制,如图 2 所示,这也会限制系统的非隔离版本。因此,这种方法可以实现更快的 SPI 时钟,但缺点是需要额外的隔离通道和 MCU 中的独立时钟移位寄存器。MCU 从二级接收寄存器读取数据,而不是标准的 SPI 寄存器。

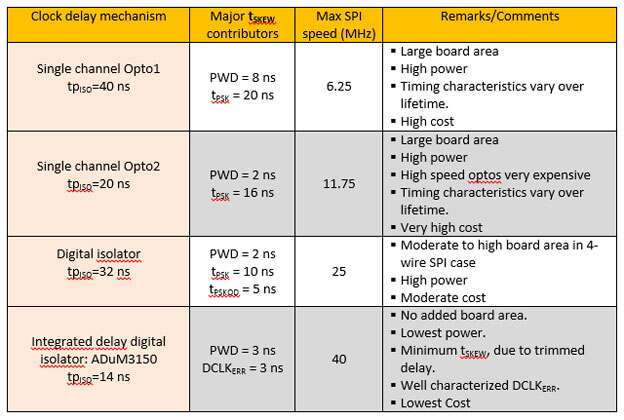

为了说明如何在不同的技术中实施这种数据传输方法,我们对以下三个示例进行了定量检查以了解速度并定性检查了功耗和所需的电路板空间。我们将看到,在标准隔离式 SPI 中,限制速度的是往返传播延迟,而在延迟时钟方案中,设置限制的是隔离器中的时序偏差和失真。

光耦合器实现

在典型的工业应用中,单通道数字光耦合器经常用于隔离高速总线。需要四个光耦合器来隔离标准的四线 SPI 总线。在估算流行的工业 CMOS 光耦合器中的 maxSPI 时钟速度时,重要的时序参数是:

为了估计 SPI 吞吐量,我们假设图 3 中不同组件的一些典型延迟。假设每个跟踪延迟为 0.25 ns,总跟踪延迟 (t TRACE) 为1ns。类似地,从设备延迟 (t SLAVE ) 和主设备设置延迟 (t MASTER ) 分别假定为 3 ns 和 2 ns。

因此,根据我们在图 3 中对隔离 SPI 时钟速率的讨论,对于使用上述光耦合器隔离的 SPI 总线,SPI 时钟周期的一半将≥ [t TRACE +t SLAVE +t MASTER +2*tp ISO ]ns 或 86 ns,给出允许的 SPI 时钟速率为 5.75 MHz。Thelong isolator prop delays 大大降低了可实现的 SPI 总线速度。

现在,考虑在反向添加一个额外的隔离器,以将隔离的时钟信号路由回主设备并实现延迟时钟,如图4所示。这使我们能够生成与从机返回的数据同步的时钟信号。隔离器的往返传播延迟 [2*tp ISO ] 不再限制时钟速率。对于系统中的剩余延迟,隔离的 SPI 半时钟周期是否可以≥ [t TRACE +t SLAVE +t MASTER ] ns 或 6 ns,支持 80 MHz 的 SPI 时钟速率?不幸的是,答案并不那么简单。

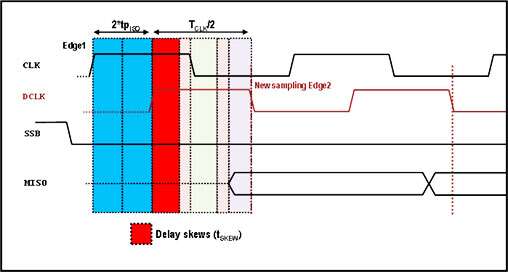

在计算图 5中显示 为 tSKEW 的 SPI 时钟周期时,仍必须考虑正向和反向通道中的不对称性。部件之间的传播延迟偏移和脉宽失真将新的 SPI 半时钟周期限制为≥[t TRACE +t SLAVE +t MASTER +2*PWD+2*t PSK ] 或 62 ns。这导致实际时钟速率为 8 MHz。然而,由于其 80 ns 的脉冲宽度限制,该光耦合器只能支持 6.25 MHz 的 SPI 时钟。上面的例子说明即使光耦合器不受其脉冲宽度的限制,t SKEW 在实际应用中,严重限制了 SPI 时钟速率,从具有完美延迟匹配的可能的 80 MHz 到 6.25 MHz。

使用更快的光耦合器和更短的脉冲宽度有帮助吗?脉冲宽度为 20 ns 的超高速光耦合器可以让我们以更高的速率运行以前的接口。但即使是这些设备也存在较大的偏斜和失真参数。在PSK 为 16 ns 和 PWD 为 2 ns 的情况下, SPI 时钟半周期变为 ≥ 42 ns,从而导致时钟速率为 11.75 MHz。在这两种情况下,光耦合器的时序特性会随着时间的推移而进一步恶化,从而在延迟时钟和从属数据之间引入更多的不匹配。为这些变化增加时序余量会导致需要进一步降低 SPI 时钟速率。

使用额外的快速光耦合器进行 SPI 隔离,除了昂贵之外,还需要大量电路板面积,因为这些器件通常是采用 SO8 封装的单通道,需要 5 个通道。隔离接口的功率预算可以高达每通道 20 mA 的电流。

数字隔离器的实现

在过去的十年中,新一代数字隔离器已经问世。这些设备具有更高的集成度、更高的速度、更低的传播延迟、低偏斜和更少的失真。考虑四通道数字隔离器。三个正向通道和一个反向通道可实现四线 SPI 总线的紧凑隔离。与光耦合器示例类似,我们从数据表中获得以下时序参数:11.1ns (90 MBPS) 的脉冲宽度、 32 ns 的传播延迟 (tp ISO )、2 ns 的 脉冲宽度失真 (PWD) 和传播延迟偏差零件之间(t P SK ) 为 10 ns。但是,与单通道光耦合器不同,在四通道数字隔离器中,还需要考虑一对反向定向通道之间的通道间匹配。在以上部分中,此参数 (t P SKOD ) 为 5 ns。

使用与图 3 相同的典型延迟,使用数字隔离器的隔离 SPI 总线的半时钟周期应≥ [t TRACE +t SLAVE +t MASTER +2*tp ISO ] ns 或 70 ns,时钟为 7 MHz。

与光耦合器情况一样,我们看到 SPI 速率受到隔离器传播延迟的严重限制。但内置标准 CMOS 技术的数字隔离器在整个产品生命周期内具有稳定的时序特性。这让我们可以设置 SPI 时钟速率,而不会为时序特性的变化留出太多余量。

考虑按照图 4使用额外的隔离器通道实施延迟时钟——至少需要使用额外的高速通道。这可以防止隔离器传播延迟限制整体 SPI 吞吐量,现在更快的 SPI 时钟是可能的,它仅受时钟和数据通道之间的不匹配和失真以及跟踪、主和从延迟的限制。给定所有隔离器通道的相似时序,对于 20 MHz 的时钟速率,新的 SPI 半时钟周期应≥ [t TRACE +t SLAVE +t MASTER +2*PWD+t PSK +t PSKOD ] ns 或 25 ns。

在许多应用中,MCU 仅从 ADC 移出数据而不会移入任何数据。在此类三线 SPI 总线中,可以使用具有两个反向通道的单个四通道数字隔离器来实现 SPI 总线和延迟时钟。在这些情况下,还有一个额外的好处。半个 SPI 时钟周期将≥ [t TRACE +t SLAVE+t MASTER +2*PWD+2*t PSKOD ] ns 或 20 ns,从而产生更快的时钟速率 25 MHz。

尽管数字隔离器的速度和偏斜明显优于光耦合器,但通道间的时序偏斜和失真仍然限制了可能的 SPI 时钟速率。用于延迟时钟的额外隔离器仍会多消耗大约 20-25% 的功率。因此,使用现有的隔离器将花费更多的功率和电路板空间,同时仍达不到该方案的可能优势。

优化数字隔离器延迟时钟实施

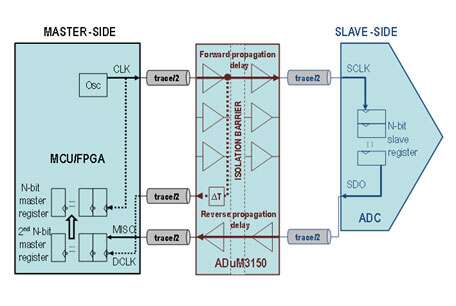

AnalogDevices 开发了一种经过优化的数字隔离器,可在延迟时钟方案中提供尽可能高的性能。ADuM3150 (图 6)是 SPIsolator 系列高速数字隔离器的一部分,旨在优化 SPI 总线的隔离。

图 6:ADuM3150 SPIsolator 延迟时钟实现

图 6:ADuM3150 SPIsolator 延迟时钟实现DCLK ERR 是延迟时钟与从机数据不同步程度的度量,因此 DCLK ERR 的符号指示延迟时钟是超前还是滞后于从机数据。由于延迟时钟用于将从机数据采样到主机中,因此它不应超前数据。DCLK 滞后数据是可以接受的,只要它不会完全错过对数据位的采样。ADuM3150 数据表规定 DCLK ERR 在 -3 ns 和 8 ns 之间,PWD 在 3 ns 之间。考虑到 DCLK ERR 和 PWD,SPI 时钟速率 ≥ [t TRACE +t SLAVE +t MASTER +(min)|DCLK ERR |+PWD]ns 或 12 ns,时钟速率为 40 MHz。ADuM3150 的数据速率为 40 MHz,能够匹配这种高 SPI 时钟速率,而不会因使用额外的隔离器通道而增加尺寸、成本和功耗。

结论

为了使过采样成为增加传感器应用动态范围的有用工具,与感兴趣的频率相比,采样频率必须有足够高的倍数,才能显着降低噪声。此处介绍的延迟时钟方案提供了提高隔离式 SPI 接口吞吐量和提高采样率的途径。

这种方法将通过可用的隔离技术提高 SPI 时钟速率。由于严格控制通道之间的偏斜和信号链中的其他失真,数字隔离技术提供了优于旧式光耦合器的显着优势。

-

使用外部 PLL 改善 FPGA 通信接口时钟抖动2023-03-14

-

数据存储在非易失性存储器中2023-03-07

-

确保电池供电的物联网传感器节点中的故障安全数据存储2023-03-02

-

一月社融数据公布,报复性消费没有如约而至2023-02-14

-

织好智能汽车数据安全防护网,任重道远2023-01-03

-

富特科技研发费用率大降:数据打架引关注,还曾沦为被执行人2022-12-23

-

蔚来突如其来的“用户数据泄露”风波2022-12-23

-

蔚来被盗,百度太贵,数据成了卡住电动车发展的新难题?2022-12-23

-

小鹏G9销售数据告诉我们,智能化虽好,但还不能将它作为主打卖点2022-12-21

-

最新汽车零整比数据显示:一个电池包等于半辆新能源车2022-11-12

-

国产电动汽车“蔚小理”发布10月交付数据 环比均下降2022-11-01

-

英威腾:公司工业自动化、新能源汽车、数据中心及光储业务都呈现增长趋势2022-11-01

-

销售数据屡创新高 中国新能源汽车积极拓展欧洲市场2022-10-17

-

多家车企9月销量数据出炉 新能源车亮点频出2022-10-10

-

中国新能源车企9月交付量数据汇总2022-10-01